System Verilog Case Statement

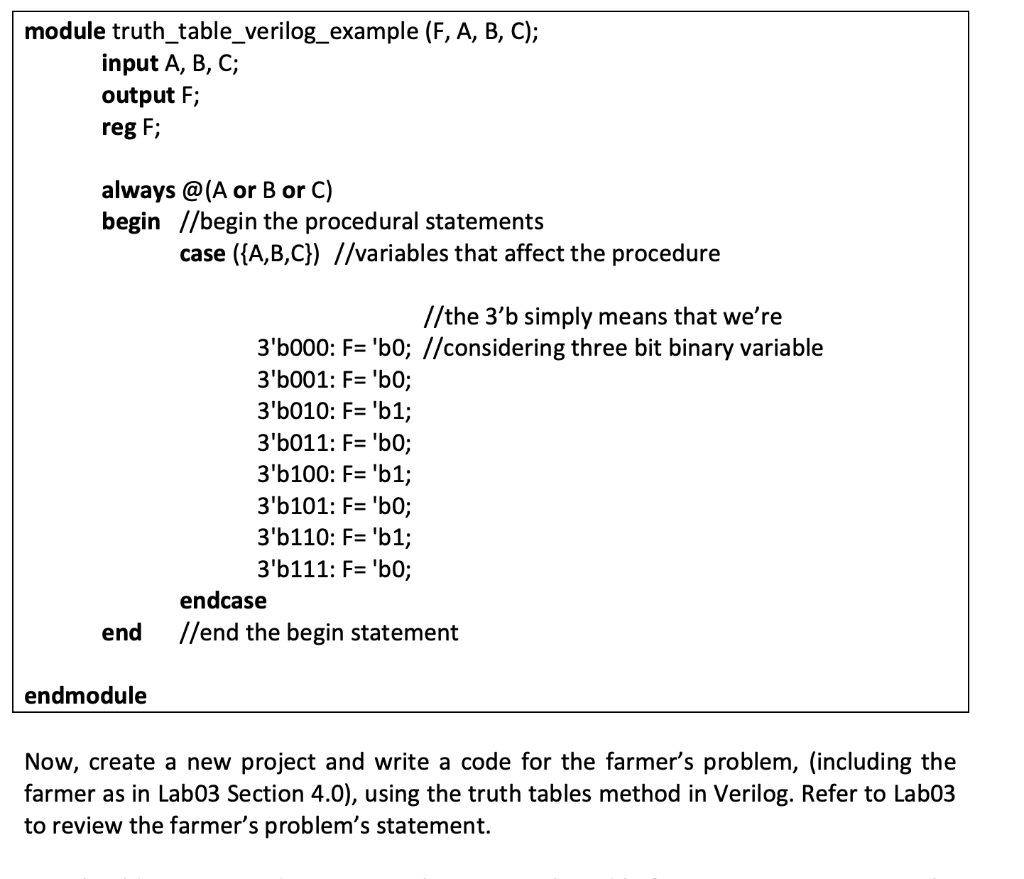

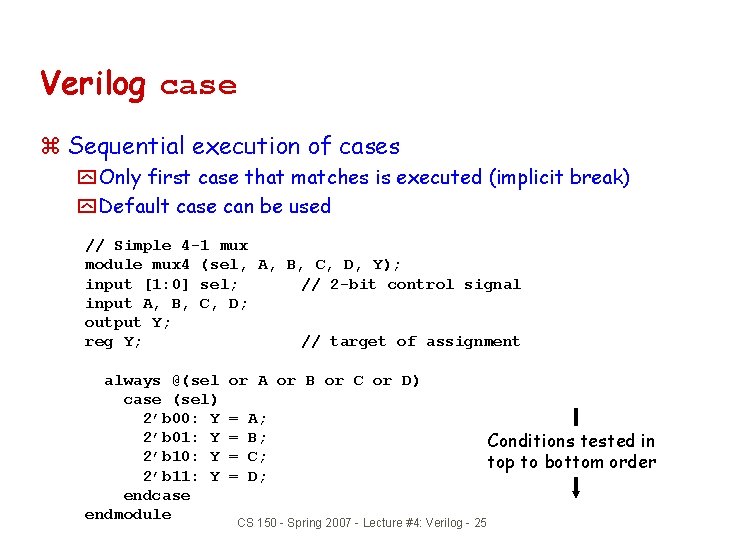

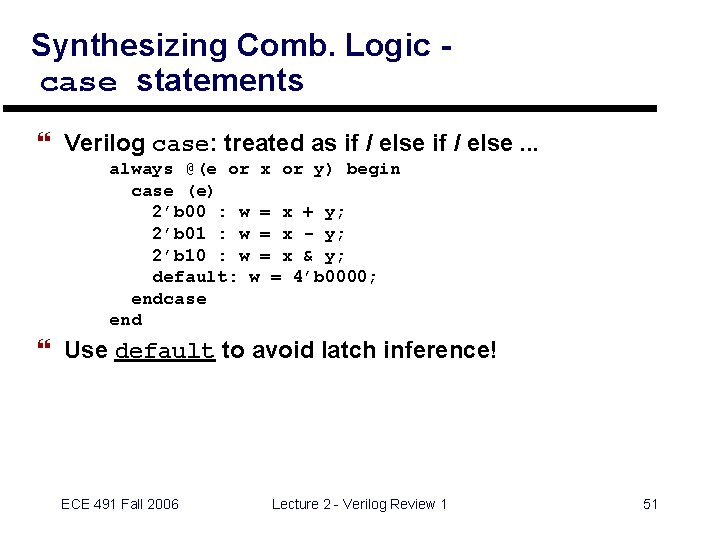

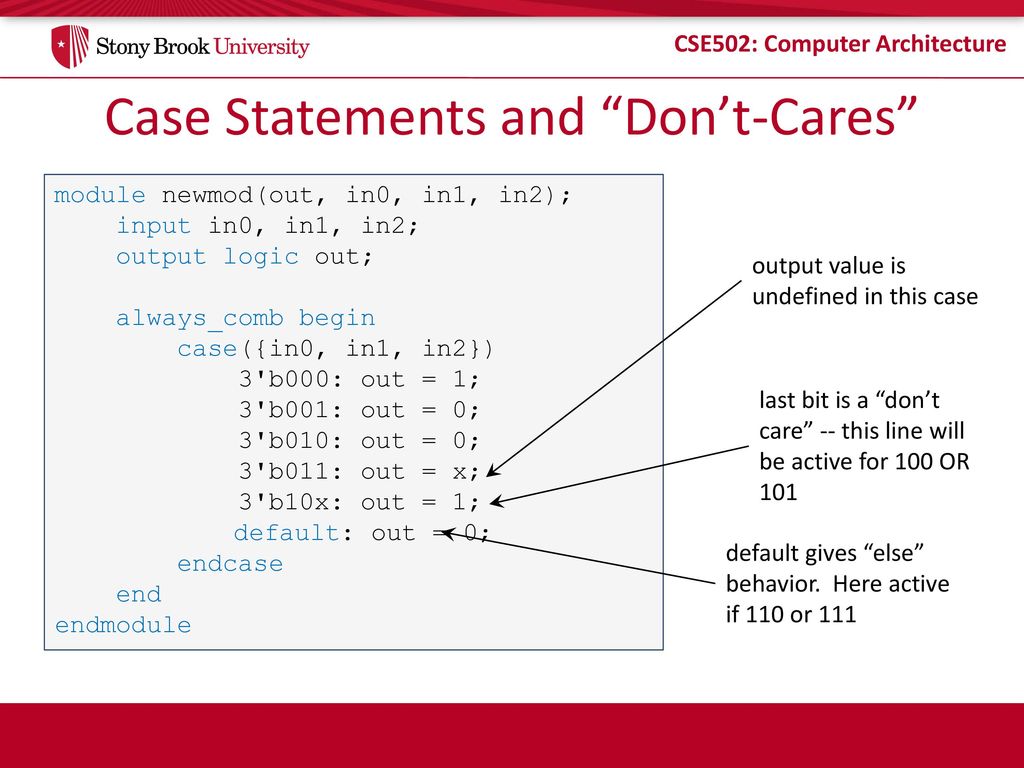

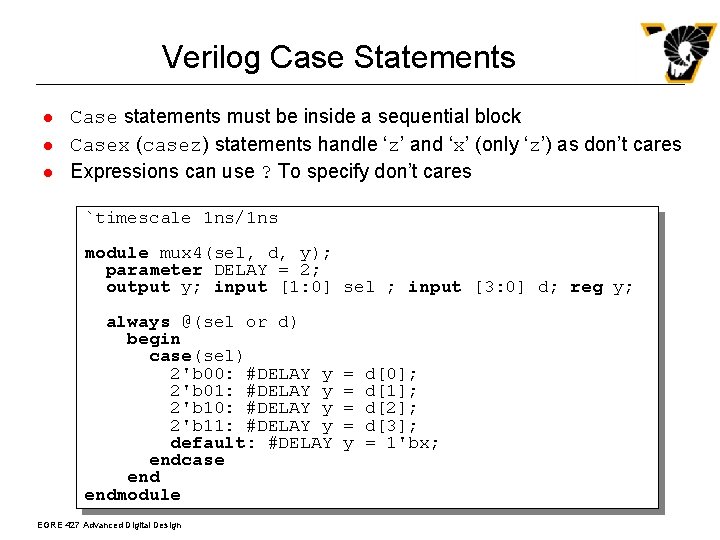

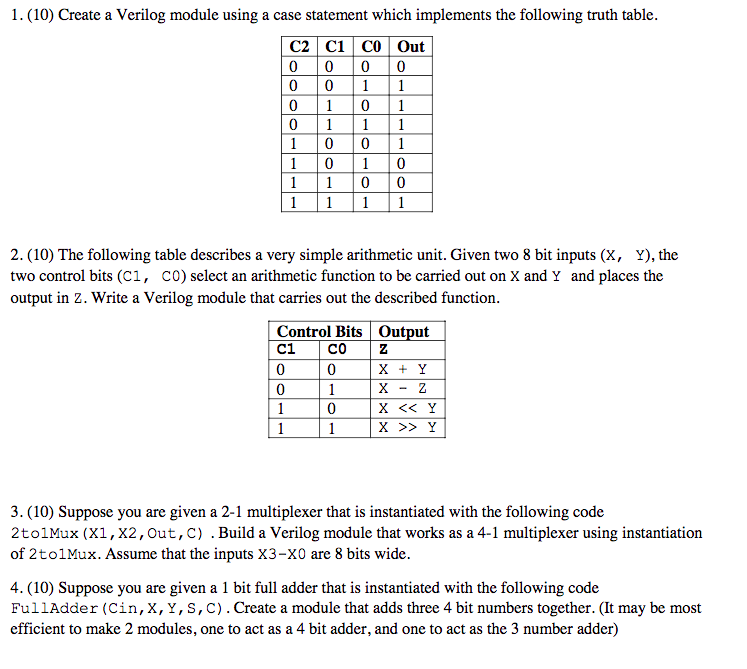

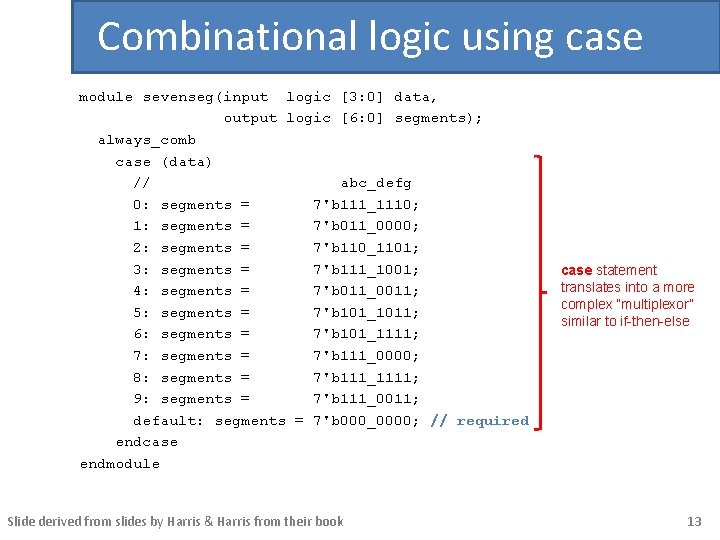

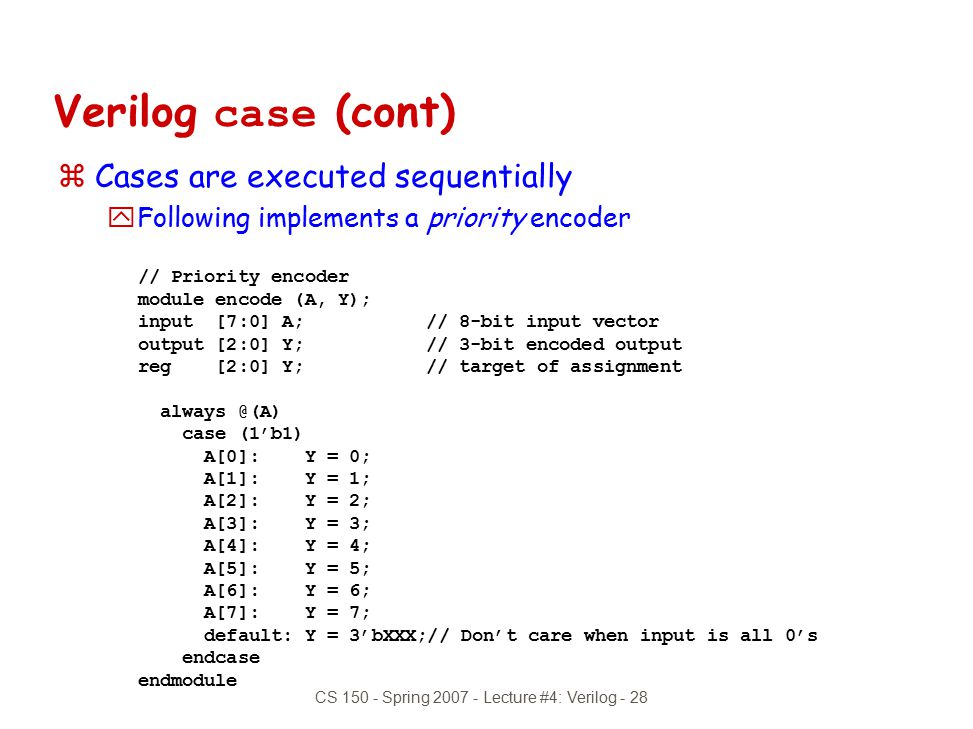

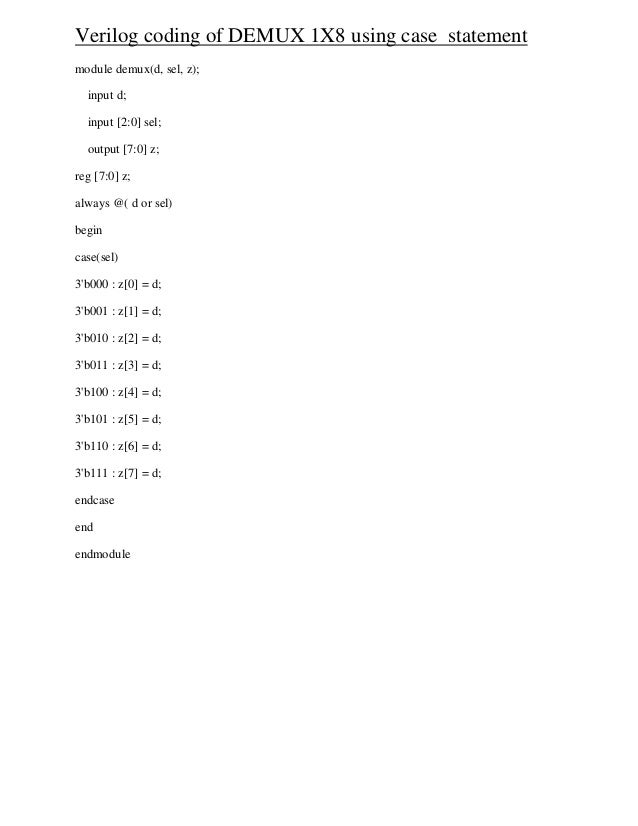

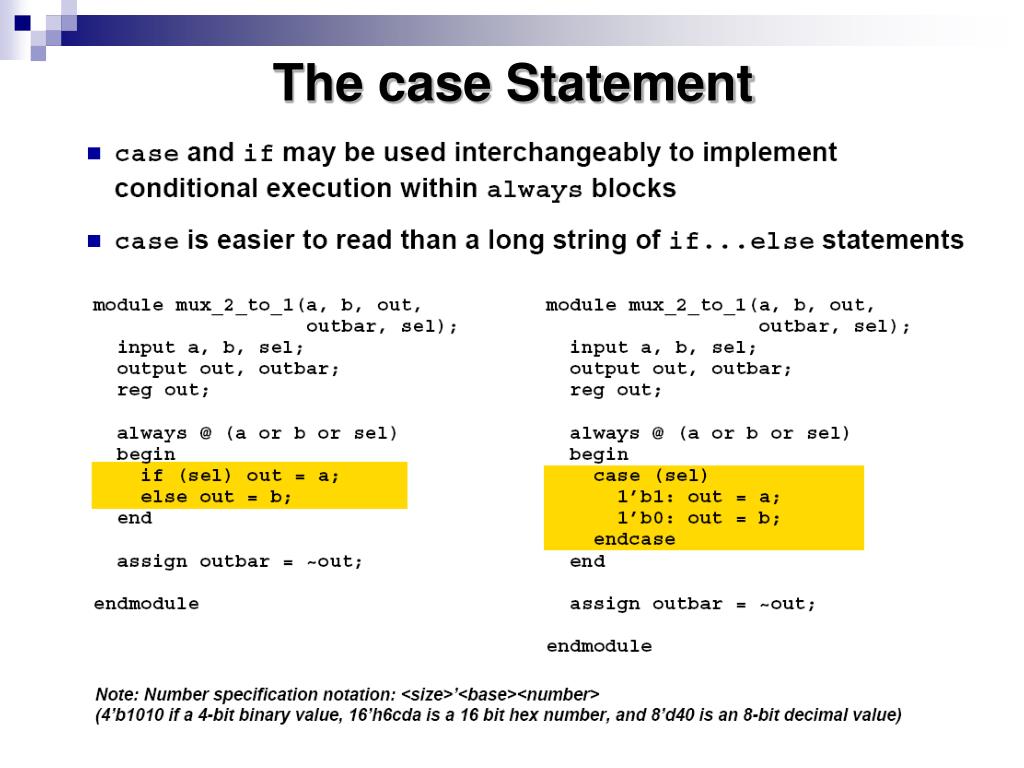

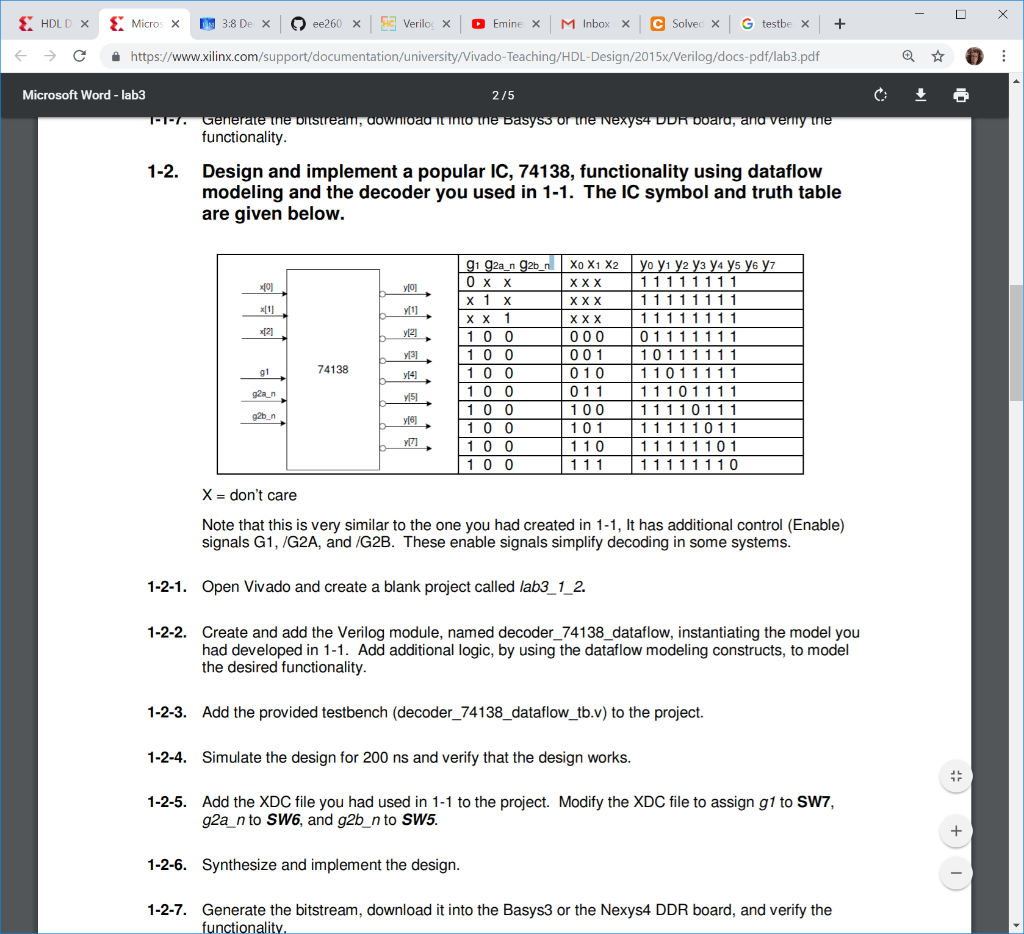

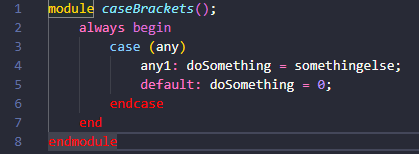

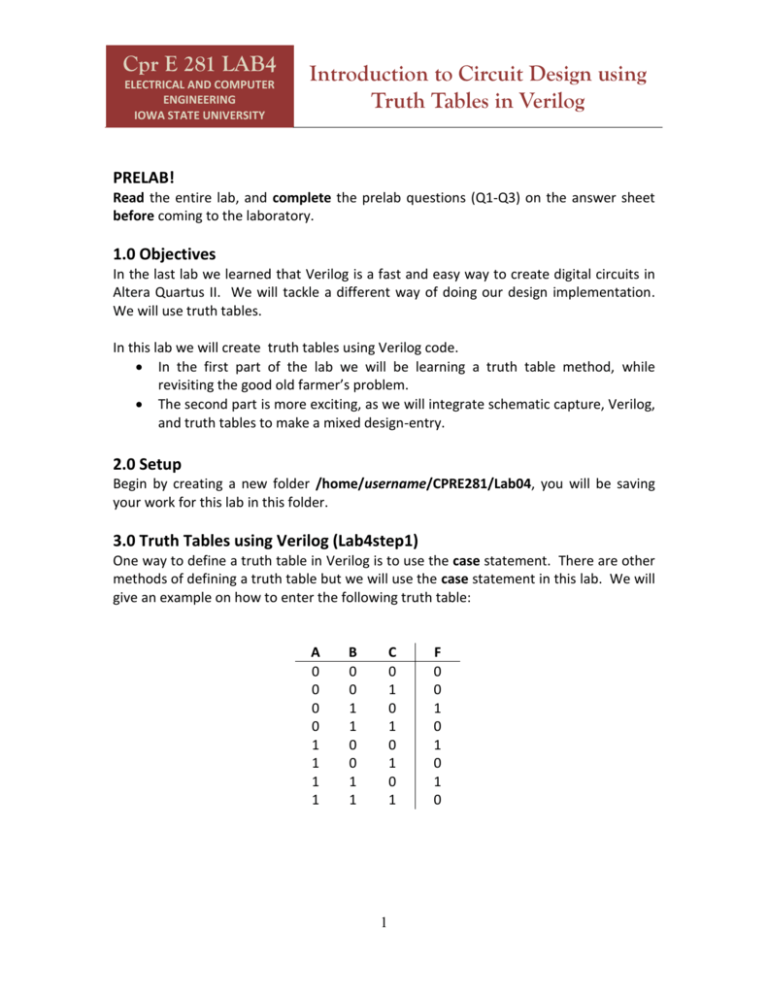

System verilog case statement. The case statement in Verilog is much similar to switch- case statement in C language. In Verilog a case statement includes all of the code between the Verilog keywords case casez casex and endcase. In other words each item is mutually exclusive and the ifelse or case statement specifies all valid selection items.

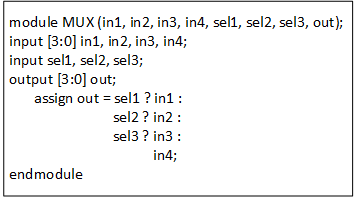

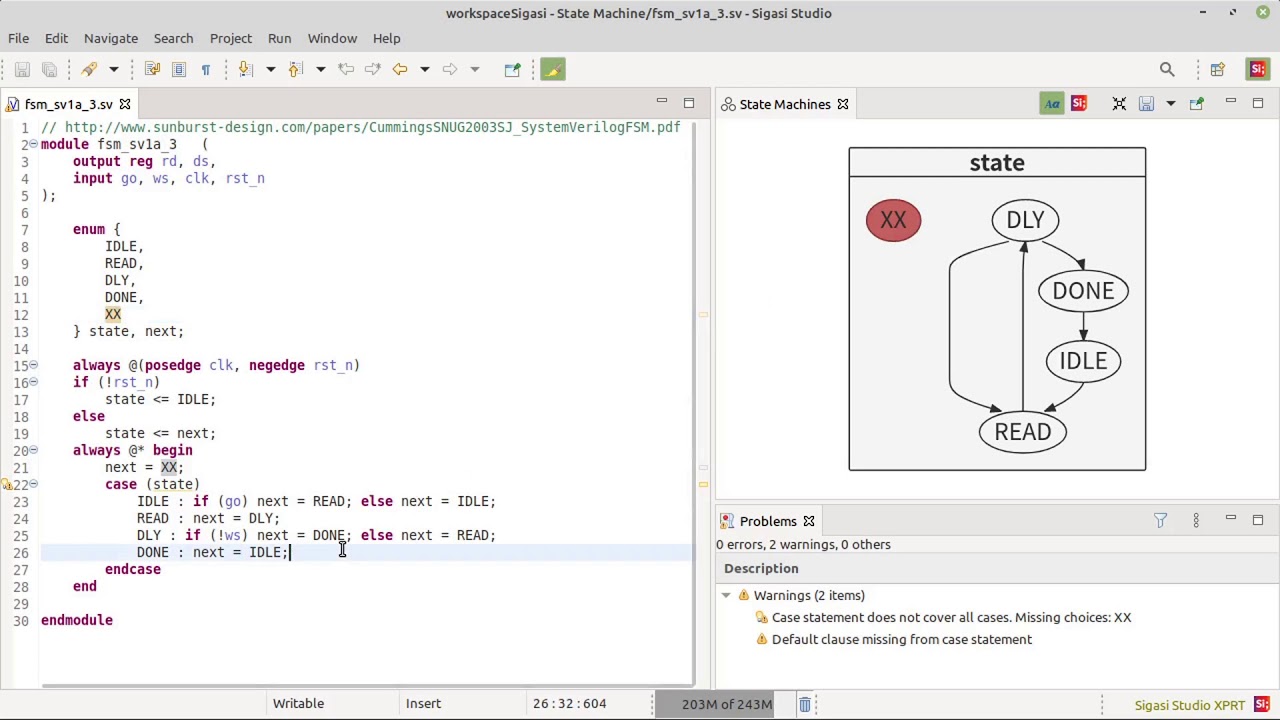

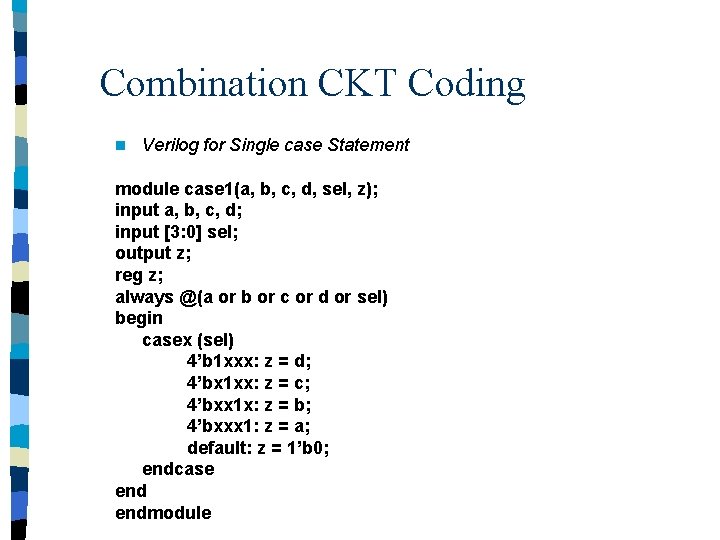

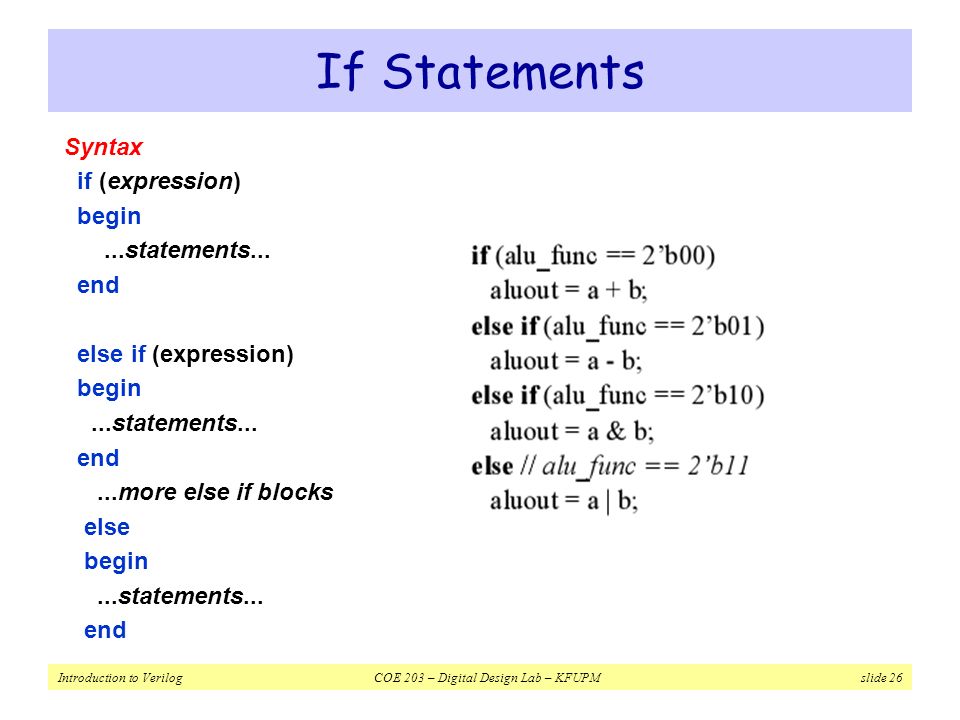

Case Statement incomplete case statement with systemverilog priority modifier module case2 input 70 a_in b_in c_in input 10 sel output logic 70 d_out. Verilog defines three versions of the case statement. The above logic can also be coded as using if else statement using a always_comb or using an assign statement using.

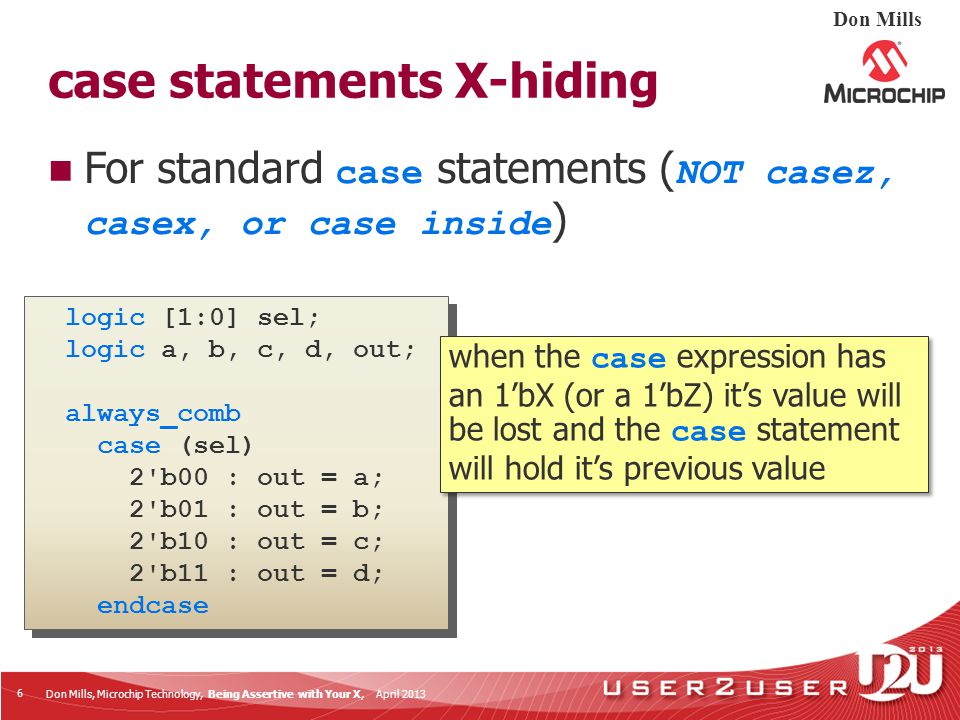

Always_comb priority case sel 2b00. Verilog is case sensitive language ie. We will first look at the usage of the case statement and then learn about its syntax and variations.

It covers a wide variety of topics such as understanding the basics of DDR4 SytemVerilog language constructs UVM Formal Verification Signal Integrity and Physical Design. SystemVerilog Case Statement. Always_comb begin ifselect 4b0001 output input_1.

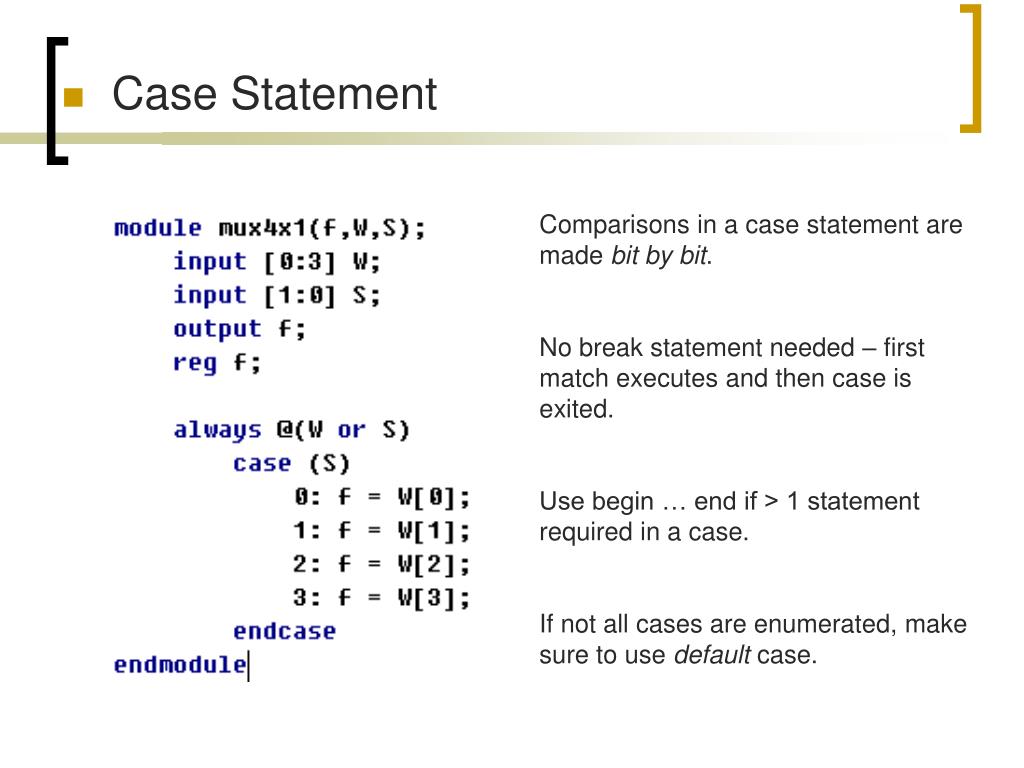

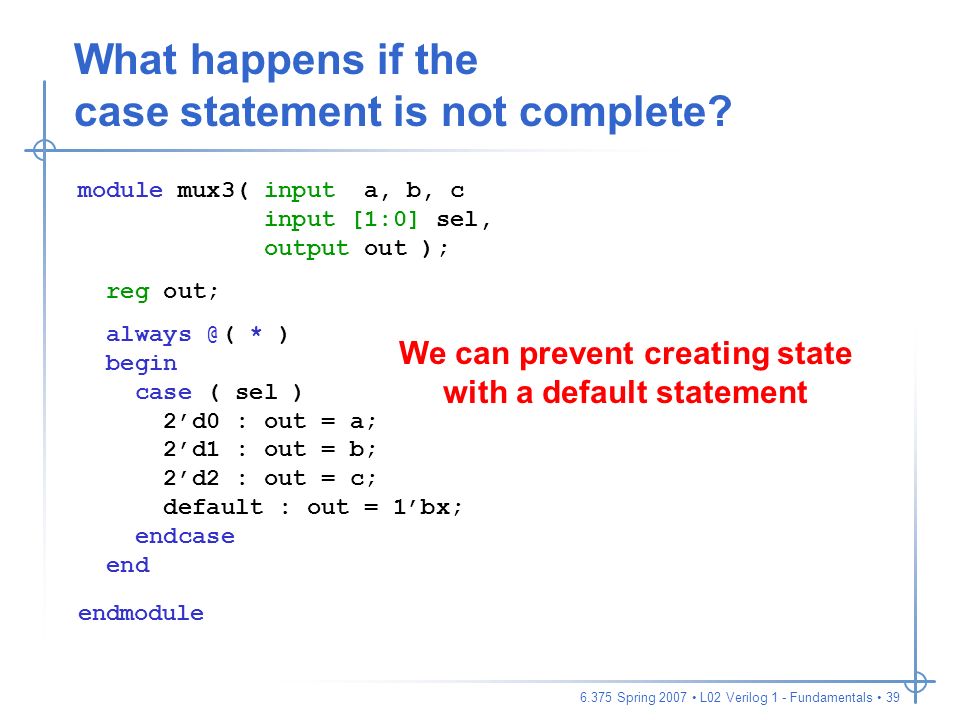

Case str abc dfg. The value of this signal is then compared with the values specified in each branch of the case statement. The case compares an expression to a series of cases and executes the statement or statement group associated with the first matching case.

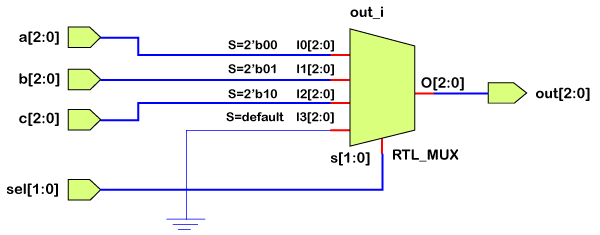

Sometimes we come across scenarios where we want the solver to randomly pick one out of the many statements. The case statement starts with the case keyword and ends with the endcase. When we write a case statement in SystemVerilog we specify an input signal to monitor and evaluate.

A case item statement is one or more Verilog statements that are executed if the case item matches the current case expression. The default branch is executed if no case items matched the case expression.

One can use the case statement to check for logic x and z values as shown in the example below.

The Verilog case statement does an identity comparison like the operator. Mealy and Moore designs. Case str abc dfg. Email to a Friend. A case item statement is one or more Verilog statements that are executed if the case item matches the current case expression. Else if select 4b0001 output input_1. In this case Mux becomes a Priority Encoded as priority of input_1 input_2 input_3 input_4. Priority encoder with casez. I Priority usage I Explicitly says that priority is important even though the Verilog case statement is a priority statement.

Given an input the statement looks at each possible condition to find one that the input signal satisfies. In programming languages case or switch statements are used as a conditional statement in which a selection is made based on different values of a particular variable or expression. A case statement can be a select-one-of-many construct that is roughly like Associate in nursing if-else-if statement. When we write a case statement in verilog we specify an input signal to monitor and evaluate. The syntax for the case statement is. A case item statement is one or more Verilog statements that are executed if the case item matches the current case expression. The verilog case statement comes handy in such cases.

Posting Komentar untuk "System Verilog Case Statement"